My dream CPU |

||||||||||||||||||||||||||||||||||||||||

CPU Architecture1. Intro

How many registers must have a CPU ? How to be organized ? What to be their purpose ?What is the minimum enough amount of registers in a CPU ? What is the usual task for a CPU ? I am not sure that existing processors are the best answer. A CPU usually is doing arithmetic, logical operations and data move. In arithmetic operations we usually have 2 input arguments and 1 result. /Trigonometric operations have 1 argument/ . Example: A + B = C; 3 + 2 = 5. And so 2 input registers and 1 result register. 2. Theoretical model

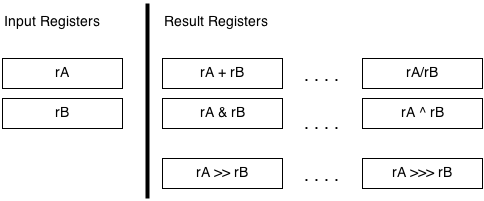

Imagine we have a CPU in which we have 2 registers for input arguments and result registers for all possible arithmetic operations.

When value in any input register is changed, all output registers are recalculated. We need only 2 instruction types: 1. Load input register from memory. 2. Store result register in memory. Input registers can be stored to. 3. Integer and Double unit

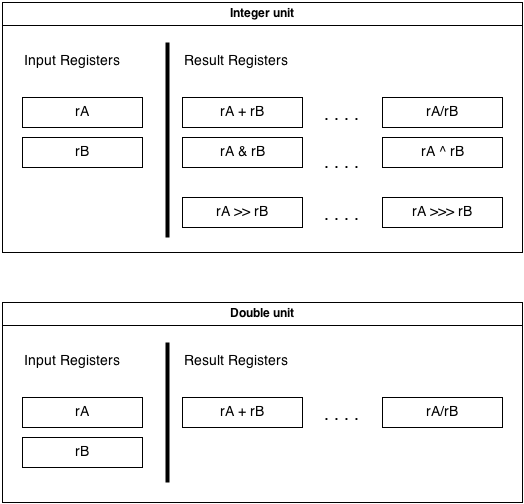

Data have different format integer and double (just any floating point format). And so we have.

Of course double unit is without logical and shift operations. 4. Address unit

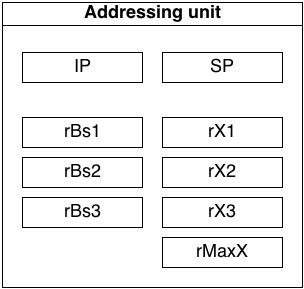

We need to something to 'walk over the memory' - address unit.Two input arguments and 1 result, this are 3 channels. One of most used data structure is the array. Array is implemented whit beginning, index of element in it and size of internal elements. For access in it is needed base register - Bs which point to beginning of the array and index register X - the offset from the beginning of the array to the element.

Index register do not contain the number of element, it contain offset from the beginning of array. Cross use between base and index register is possible.  If value in rBs1 or rX1 is changed, immediately start calculation for rBs1 + rX1 in hidden register. This calculation is in parallel with all other and there is no time lost. The same is for all other base and index registers. 5. The whole CPU

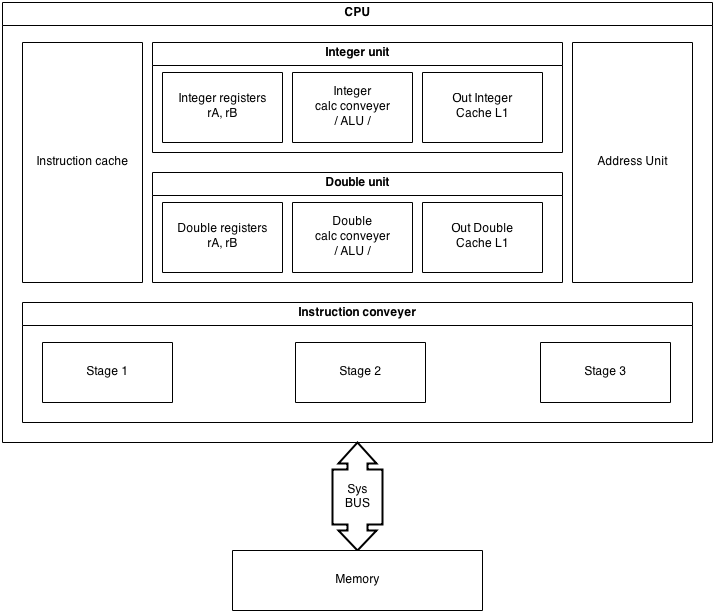

1. Instruction cache contain all loaded instructions 2. Integer Unit: - Integer registers rA and rB - Integer ALU - Cache for integer results 2. Double Unit: - Double registers rA and rB - Double ALU - Cache for Double results 3. Address unit contain all registers for addressing and IP - instruction pointer and SP - stack pointer. 4. Instruction conveyer contains 3 stages: - Stage 1 - read the instruction and operand - Stage 2 - executes operation. - Stage 3 - stores result back in memory. Memory --> Register operations uses stages from 1 to 3. Register --> Memory operations uses stages from 1 - 4. 6. Hello World

All instructions are about Int conveyer - I: prefix The first column - "0, 2 ,4 " are the number of lines. Every instruction is 2 memory lines, instruction and operand. More info about CPU instructions |