- 1. Intro

- 2. Instruction format

- 3. Addressing methods

- 4. Instructions by Conveyers.

- 5. Register to register instructions RR

My dream CPU |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Assembler instructions in RCPU1. Intro

2. Instruction Format

3. Addressing Methods

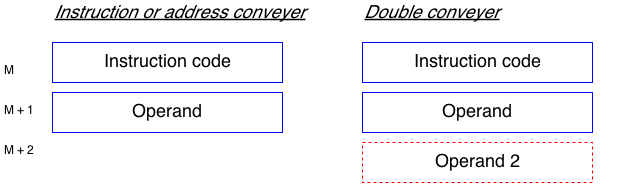

4. Instructions by Conveyers

4.1 Integer Conveyer

4.1.1 Memory --> Register MR

Move data from Memory to integer register. Load integer register from memory. Registers are rA and rB.

4.1.2 Register --> Memory RM

Move data from integer register to Memory. Store integer register in memory.

It is just a kind of interpretation. Are they registers (read only) or instructions. Here is possible only Absolute and Index addressing.

4.2 Double Conveyer

4.2.1 Memory --> Register MR

The instructions are the same as in Integer conveyer. Instead prefix 'I' using 'D'.

4.2.2 Register --> Memory RM

The instructions are the same as in Integer conveyer. Instead prefix 'I' using 'D'.

Logical and Shift operations do not exist here. 4.3 Address Conveyer

Addressing methods:

Here are possible only direct and absolute addressing methods.

Registers:

4.3.1 Memory --> Register MR

Move data from Memory to address unit register. Load integer register from memory.

4.3.2 Register --> Memory RM

Store data from register to memory.

5. Register --> Register RR

Move data from register to register. When move data from double to integer register, take int part only.

Source --> Destination Conveyer : Register --> Conveyer : Register

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||